近期,一则来自韩国媒体的报道指出,Intel的18A工艺良品率仅为10%,此消息一出便引起了广泛关注。然而,Intel官方并未直接公布这一具体数据,那么实际情况究竟如何呢?通过一些公开信息和计算,我们或许能窥见一二。

首先,值得注意的是,在半导体行业,台积电与三星作为代工领域的两大巨头,它们之间的竞争异常激烈。因此,关于对方的负面消息往往成为媒体关注的焦点。此次关于Intel 18A工艺的报道,其背景也值得我们深思。

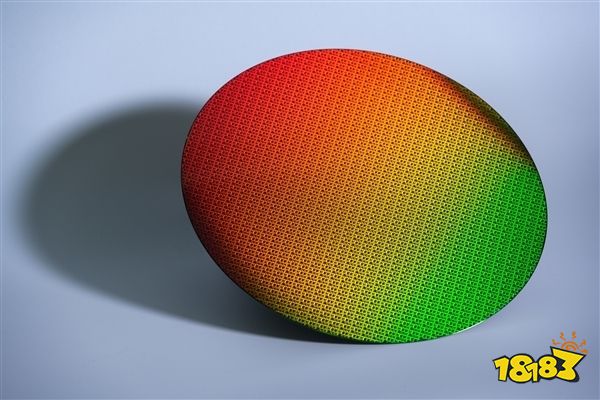

良品率,作为衡量半导体生产工艺好坏的重要指标,其影响因素众多,不仅与工艺本身有关,还与所生产的芯片类型密切相关。例如,手机芯片与AI芯片在相同工艺下的良品率往往存在显著差异。

以NVIDIA的H100芯片为例,其面积高达814平方毫米,几乎触及了光罩的极限(858平方毫米)。如此庞大的芯片面积,无疑对良品率提出了极高的挑战,这也是其价格居高不下的重要原因之一。

今年9月初,Intel官方曾宣布,18A工艺的缺陷密度(D0)已降至0.40,达到了量产的标准。并计划于2025年推出基于该工艺的消费级Panther Lake和数据中心级Clearwater Forest产品。如今,时隔三个多月,我们有理由相信,Intel在进一步优化工艺,降低缺陷密度方面已取得了新的进展。

为了更直观地了解18A工艺的良品率情况,我们可以借助一些专业的计算工具进行估算。以SemiAnalysis的良品率计算工具为例,它支持多种计算模型。假设我们使用Intel 18A工艺生产858平方毫米的极限尺寸芯片,根据最乐观的Seeds模型,良品率可达22.56%;而按照最差的模型计算,良品率也有3.23%;默认Murphy模型下的良品率则为7.95%。然而,实际生产中,如此大尺寸的芯片几乎不太可能采用18A工艺。

更具参考价值的是,网上曾泄露过Panther Lake内核的照片及精确尺寸。据此,我们可以计算出其计算模块(预计采用18A工艺)的面积为114.304平方毫米。通过计算工具估算,默认模型下的良品率为64.4%,最高可达69%,即便在最差的情况下,良品率也保持在50%左右。对于更小面积的GPU模块(假设为53.6平方毫米),良品率更是最高可超过82%,最低也不低于60%。

此外,虽然有报道称博通早期对Intel 18A的良品率表示失望,但这可能只是工艺初期的暂时现象。随着Intel对工艺的不断优化和提升,我们有理由相信,到明年量产时,18A工艺的良品率将能够满足客户的需求。

综上所述,关于Intel 18A工艺良品率的争议,其实并不简单。通过公开信息和计算工具的估算,我们可以得到一个更为全面和客观的认识。而最终的良品率表现,还需等待实际量产后的市场检验。

0

0