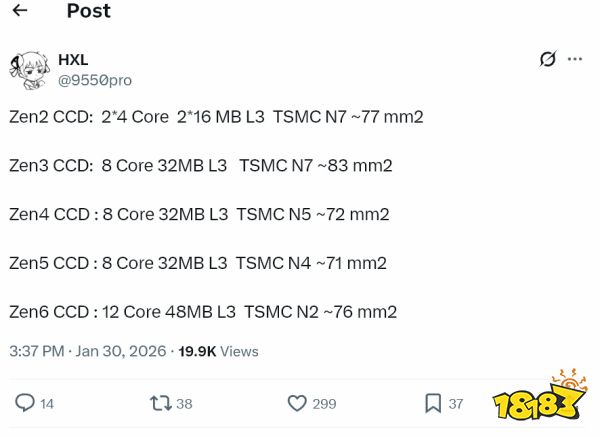

AMD锐龙处理器即将迎来问世十周年,其核心的CCD架构也正进入重大变革阶段。据悉,今年将推出的采用2nm工艺的Zen6架构,其CCD计算核心将首次升级至12核心,这标志着自Zen架构问世近十年来的第二次大规模CCD设计革新。

在年初的CES展会上,AMD正式宣布了面向服务器与AI市场的Zen6架构EPYC处理器产品线,代号Venice。该系列专注于高性能与吞吐量,相比前代线程密度提升30,性能与能效提升高达70。服务器版Zen6最多将支持256个核心。

面向桌面平台的Zen6处理器代号为Olympic Range。据爆料,其CCD核心将升级至12核架构,并配备高达48MB的L3缓存,相比当前的Zen5提升达50。尤为关键的是,在2nm先进工艺支持下,核心面积仅从上代的71mm²小幅增加至76mm²,面积效率极为出色。

这一CCD规模升级是Zen系列历史上幅度最大的一次。主流桌面平台采用双CCD配置即可轻松实现24核心与96MB L3缓存,更高端的配置可实现48核心与192MB L3缓存。对于X3D系列,每个Zen6 CCD还可通过3D V-Cache技术额外堆叠缓存,使每个CCD最多搭配144MB L3缓存,双CCD配置下可达288MB。

考虑到英特尔预计在明年上市的Nova Lake-S桌面处理器也传闻将拥有多达288MB缓存与52个核心,AMD与英特尔在高端桌面处理器,特别是发烧级游戏CPU市场的竞争势必日趋激烈。Zen6架构的推出,预示着下一代处理器性能与规格大战的序幕已经拉开。

0

0